1 概述

ANSYS Totem是晶体管级电源可靠性、噪声和可靠性仿真平台,该平台可以使您的IP、模拟、混合信号设计和全定制数字设计满足越来越严格的电源完整性及可靠性要求。Totem具有SPICE级别的分析精度,并支持在分析时纳入封装以及衬底寄生。

Ø 完整的解决方案

Totem支持用于模拟、LEF / DEF(用于数字)的主要数据格式(GDS,OASIS,LVS数据库等),并且与主要的spice仿真环境兼容。它具有处理非常大的设计的能力,并具有出色的宏建模功能,可以为SOC signoff生成准确而紧凑的IP模型。

Ø 一流的Signoff Analysis

Totem的提取、模拟、电迁移和自热分析核心引擎均通过了主要技术节点的认证,并多次与Spice和硅测量结果进行了关联。Totem已通过多家主要铸造厂的认证,并且是多家主要半导体公司的首选signoff工具。

Ø 广泛的设计范围

Totem提供了涵盖从早期到signoff的全面分析套件。它可以有效地处理各种设计风格,例如SerDes,数据转换器,电源管理IC,嵌入式存储器,DRAM,闪存,FPGA和芯片图像传感器。此外,它还提供多种分析功能,包括基板噪声分析,RDSON分析,热和ESD分析,以应对不同设计中的挑战。它还为客户提供了一个可配置的座舱,可根据工作流程自定义其分析。

2 功能特点

Ø 经硅验证的模拟及混合信号EM/IR设计signoff

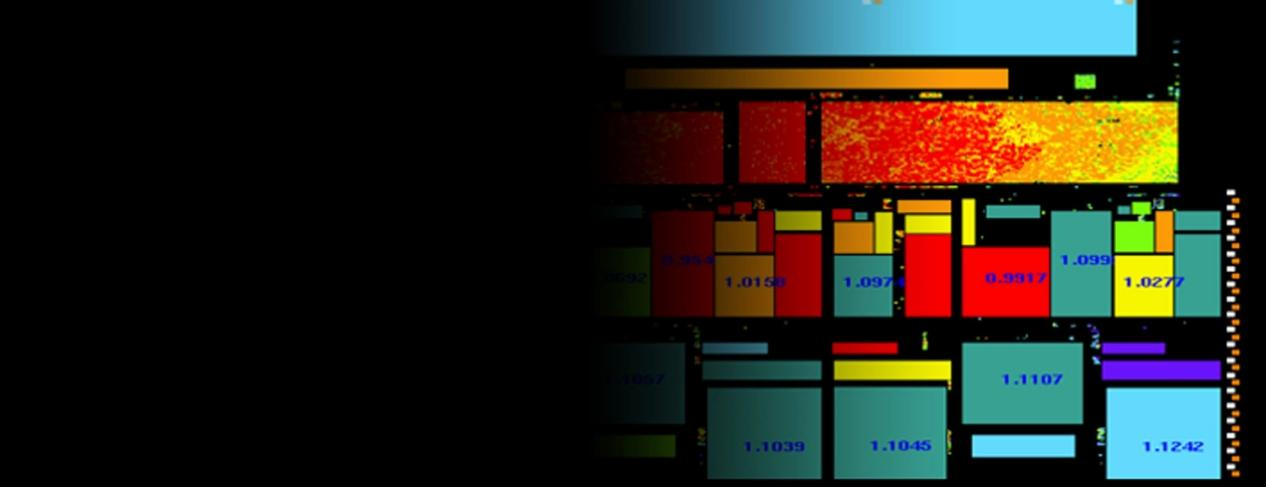

Totem静态分析可帮助您验证IP及全芯片设计的电源地网络的鲁棒性。动态电压降分析可暴露因局部晶体管同时开关而导致的设计缺陷,并可反映实际的电路操作以及因此引起的包括变化的电流需求,及其与电源网络的电容及电感寄生的相互影响——可能导致电源电压下降或接地电位反弹。

Totem可以分析从系统/PCB到片上电源地及衬底的整个电源地分配网络上的噪声传播。多个客户对硅实测值和Totem的仿真结果进行过验证并高度认可,这充分证明了Totem的精确度。硅实测和仿真结果验证包括从IP到全定制芯片,工艺节点也扩展到涵盖目前先进的技术节点,包括7nm。

Totem是业界优秀的模拟及混合信号电源噪声完整性及可靠性设计交付解决方案,所有的大型半导体公司在生产流程中都会使用,这无疑是对Totem精确度的进一步认可。

Ø 早期和设计中分析

在模拟和混合信号设计中,通常认为EM和IR分析尽可能接近录音带。这是由于传统工作流程的基本局限性所致,要求设计必须保持LVS干净以执行提取,仿真并获得可靠的EMIR结果。但是,随着设计周期的缩短,在设计过程的早期阶段就越来越需要进行设计内分析。这是由于技术的扩展,导致更薄的互连表现出更高的寄生电阻,更低的EM容限,更高的功率密度和更低的工作电压。

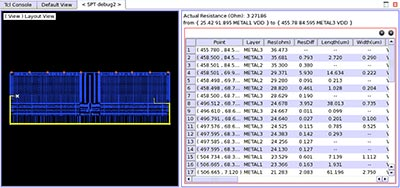

Totem提供了各种功能,例如电网缺陷分析,缺少通孔,P2P检查以及各种早期的静态和动态IR和EM分析,这些功能可以突出设计缺陷,而这些缺陷的成本很高,难以解决贴片问题。这些内容以直观和用户友好的方式呈现给设计人员,使他们可以做出关键的设计决策,例如电网规划,凸块放置,去耦电容帽优化,关键网络上的EM等。

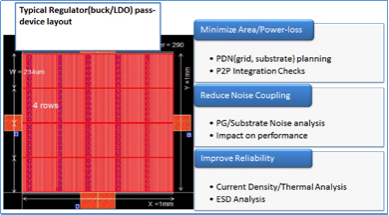

Ø 电源管理芯片的分析

移动及IoT设备的爆炸性增长以及这些设备对能耗效率要求的提高推动了对电源管理IP的需求。任何可能导致局部电流密度增加、电压下降或噪声耦合的设计缺陷都会影响电力配送。因此,设计人员必须找出此类缺陷,尤其是特定于电源管理电路的缺陷。因为电源管理IP广泛应用于全芯片集成的多种功能模块,设计人员必须在全芯片设计的背景下看待这些缺陷,这无疑更具挑战。

Totem是适用于全芯片模拟、混合信号I/O设计的电压降、可靠性(EM/ESD)及噪声耦合分析的综合性仿真平台。同时针对电源管理芯片,Totem可以对电阻、电流密度及保护环这些重要项目进行分析,确定设计缺陷。此类验证既可以在PMIC模块或IP的设计阶段完成,也可以在全芯片顶层级别的集成阶段完成。

Ø Signoff分析

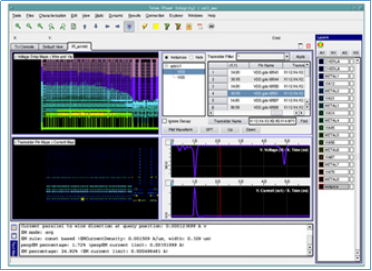

选择正确的矢量来给电网施加压力是一个挑战,因此设计人员可能经常会运行更长的仿真来涵盖更多场景。在整体模拟中包括电网复杂性会大大增加传统流程的分析时间,而传统流程耗时数天至数周。这使得任何ECO更改都变得不可能,并可能导致昂贵的金属重制,甚至导致硅产量问题。

Totem提供了多种选项,可以对大型混合信号设计进行准确的签核。诸如布局和路线数字数据库的本地处理以及复杂AMS的层次分析之类的关键功能通过促进自下而上的汇总视图,极大地简化了总体流程,在该汇总视图中,块所有者可以对其块进行全面验证并汇总一个全面的多状态晶体管顶级分析的抽象级别或抽象宏模型。在将几个模块与数字位置和路线数据集成在一起的同时,仿真可以利用并对齐子模块的不同功能状态,以模拟几种可能给电网带来压力的最坏情况。

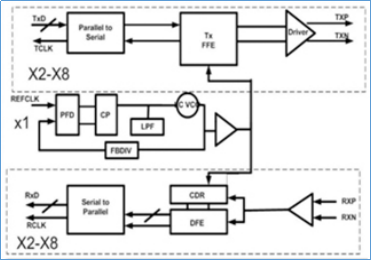

复杂混合信号接口的经典示例是PHY接口。串行接口(又名SerDes)可以分为定义明确的子块,如时钟和数据片。可以将它们分析并建模为宏模型。这些宏模型可以保留完整的,未降低的电网,直至器件扩散,以及详细的多状态电流曲线,为不同的功能状态建模。此外,接口中的任何数字模块都可以使用向量(VCD / FSDB)或无向量的方法进行详细建模,直至标准单元级别。完整的IP级别分析需要将这些时钟和数据切片视图结合起来,并包括封装模型以执行详细的瞬态电压降分析。Totem分析了噪声在整个功率传输网络中的传播情况,从封装到芯片上电网和基板网络,整个功率传输网络都在传播。

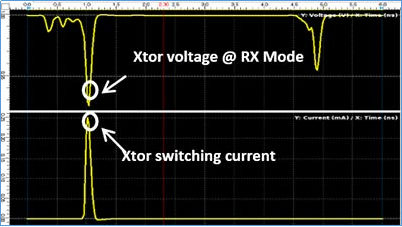

Ø 高速千兆SerDes IP分析

由于高速SerDes的性质,抖动(影响错误率)、功率(影响每比特能量)以及可靠性(影响集成电路的长期操作)是设计师经常面临的挑战。使用先进的制程技术导致电流密度增加,同时结合热的因素会极大地影响电源完整性以及 EM可靠性问题,这进一步增加了设计障碍难度。为了尽可能降低故障风险,必须对SerDes IP从内部每个单独模块到整个IP针对电源噪声以及可靠性问题做检查。

Totem提供一个综合性的仿真框架,适用于模拟、混合信号 I/O 设计的电压降、衬底噪声、可靠性(EM/ESD)及噪声耦合分析。此外,Totem可生成SerDes IP电源模型用于顶层设计分析,以实现全覆盖的芯片压降、电迁移以及ESD完整性分析。这些模型增加了SerDes在全芯片级分析时的功耗特征可信度和覆盖率。

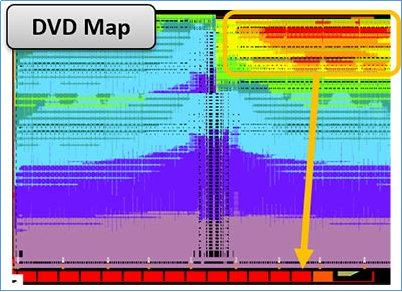

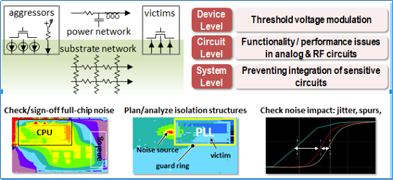

Ø 衬底噪声分析

电路中常见的是来自于高速数字电路的噪声到敏感的模拟及RF块的噪声耦合。这需要展开真正的模数混合电源噪声及可靠性分析。

Totem具有晶圆代工厂确认的具有成功流片案例追踪记录,用于衬底噪声分析签核的混合信号EM/IR工具,它可以帮助您进行噪声时域、频域分析及评估保护环质量的影响,从而加快设计交付。

NXP利用此功能将多个无线电集成到单个芯片上,同时尽可能地降低了来自片上高速数字信号的衬底噪声。他们的分析结果也与实际硅片结果匹配的很好。

Ø 高级调试

根本原因分析以及假设性修复是任何分析工具都应具备的重要功能,尤其是关注降低噪声容限、增加热效应并尽可能减少封装及PCB寄生效应的电源噪声完整性及可靠性解决方案。在包含数字、模拟及RF信号的混合信号芯片上,复杂性更为突出。

Totem基于布局的分析以及内置图形化界面通过将仿真结果叠于布局之上,全面直观地显示故障原因,这便于您快速展开交互式根本原因分析以及假设性修复,进而显著缩短调试周期。

Totem的通用、多功能图形化界面的外观和感觉类似于版图编辑器,并通过精密的多选项卡、多窗格功能提供对仿真结果的完全可视性。

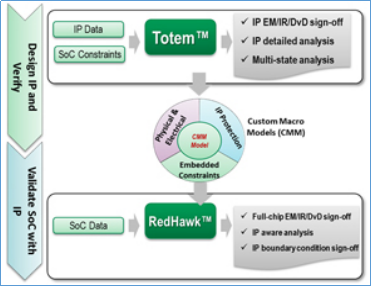

Ø IP signoff及SoC集成

IP是每个SoC设计中不可或缺的一部分。无处不在的连接性需求已经推动SoC中的集成程度甚至已经超越摩尔定律的预测范围。IP不仅需要在独立模式下工作,还需要同其他第三方IP一起集成于目标SoC之后的复杂电路环境中工作。IP集成及验证被视为SoC设计师面临的几个严峻的挑战。芯片顶层压降分析时,同一IP在两种不同的工作模式下操作,电压降可能迥然不同。为确保IP在SoC中电源完整性,设计师必须精确建模并描述IP在不同操作模式下的特性用于顶层电压降分析。将IP移交给SoC团队时,提交的数据也必须包括IP的电气及物理属性,以及电源完整性签核限制参数等信息。

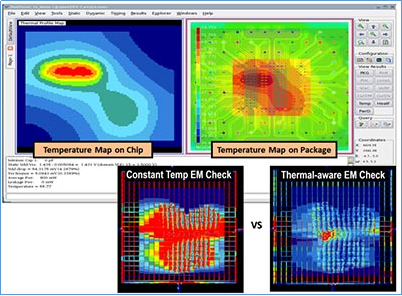

Ø 先进的可靠性分析

尽管FinFET在面积,性能方面具有多个优势,但FinFET设计上的局部热梯度可以达到器件上高达30摄氏度的温度,这主要归因于FinFET超薄,高电阻互连的3D特性以及导热性差的电介质。Totem提供了全面的EM signoff,包括电源/信号EM分析,建模焦耳加热,FinFET的导线耦合和自热以及它们对互连的影响。主要代工厂均已启用该流程,进行FinFET设计的客户均使用该流程。Totem还启用了统计EM预算编制功能,可以满足汽车和其他关键任务应用程序的需求。

首页 > 产品中心 > 半导体仿真

首页 > 产品中心 > 半导体仿真