1 概述

ANSYS RedHawk-SC是一款适用于SoC设计的行业标准电源噪声和可靠性签核解决方案。RedHawk在芯片设计方面成绩卓著,支持您构建高性能、低能耗的SoC,可有效解决移动、通信、高性能计算、汽车和物联网(IoT)等市场中的热、电迁移(EM)和静电放电(ESD)问题。

RedHawk-SC是基于Ansys SeaScape构建的下一代解决方案,Ansys SeaScape是一个针对电子系统设计和仿真的定制设计的大数据架构。SeaScape提供了每核可扩展性,灵活的设计数据访问,即时设计启动,支持MapReduce的分析以及许多其他革命性的功能。

Ansys RedHawk-SC是用于下一代设计的电源噪声和可靠性验收的新标准,已经过生产验证和硅验证。底层的弹性计算体系结构具有可扩展性,可以在几个小时内解决大的芯片。大数据分析可实现快速的数据挖掘,以推动可行的结果和优化。RedHawk-SC可以在一夜之间探索成千上万种切换方案,并通过分析多个不同的参数确定大量矢量集的优先级。RedHawk-SC专为多站点协作而构建,使您能够同时查看,调试和浏览设计和仿真数据。使用RedHawk-SC,您可以在几秒钟内加载大的设计,运行复杂的多变量分析,推动设计优化并更快地完成设计。

2 功能特点

Ø RedHawk-SC关键功能

· IR压降分析

· 热感知EM 分析

· 电压变化的时序影响分析

· 矢量和无矢量活动

· 芯片/封装电热协同仿真

· 云弹性计算

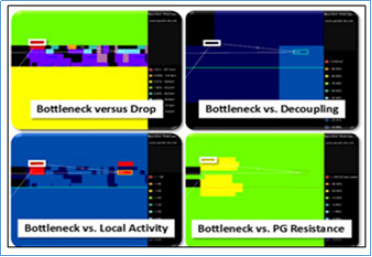

· 先进的 root-cause和ECO 分析

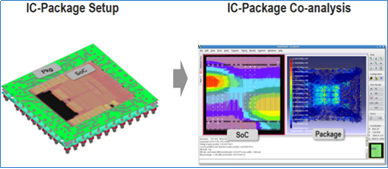

Ø 芯片封装协同分析

在针对移动手机或服务器的电子系统中,处理器和存储器等IC负责执行应用程序和数据处理功能,消耗的功率最多。这些IC与它们的I/O电路之间输入/输出的数据量最大,并且产生的有害功率、热量以及EMI信号也最大。

IC消耗的功率与其电源电压直接相关。由于阈值电压不会一同缩放,电源和阈值电压之间的差距缩小,从而降低了噪声容限。

随着技术的发展,由于封装阻抗日益增加,对降低成本和能耗的需求使芯片和封装级别的供电网络(PDN)设计变得复杂。这减少了电压,对芯片而言成为有害级别。

RedHawk-CPA支持您无缝导入封装布局,以及针对封装感知和精确的片上静态IR降以及交流热点分析考虑去耦电容和电感。

Ø 热感知EM

ESD及电源/接地和信号EM是亚16nm级别迫切需要解决的两个可靠性问题。EM和ESD分析的精确度以及覆盖率极为重要。随着导线中的电流增加,工作电压会降低,EM范围会缩小。由于FinFET的使用,自热被添加到热问题中。在汽车等众多应用领域,了解、分析并优化每个IC设计以便实现正确热行为至关重要。

RedHawk为热感知电源/接地和信号线EM验证提供全面支持,在尽量减少误报的同时准确分析EM冲突,即使是基于FinFET的先进设计亦可从中受益。在与ANSYS PathFinder结合使用时,RedHawk可以执行SoC级别ESD完整性分析,从ESD事件(HBM、CDM)为所有电流通路(导线和过孔)提供连接性和互连故障检查。RedHawk在电源EM、信号EM和SoC ESD签核方面获得芯片代工厂认证。

Ø 容量和性能

目前的片上系统(SoC)拥有更大规模的整合内容,并且采用先进的工艺技术。因此,必须考虑的设计参数的数量正在迅速增加。这为执行分析带来了性能瓶颈:最好的情况是要运行数天,最坏的情况是根本无法运行。

RedHawk采用先进的分布式机器处理(DMP)技术,可为您提供模拟包含10亿多个实例的设计所需的大容量和高性能。DMP拥有的签核精确度仅可通过扁平仿真获得。

DMP还利用私有机器群集不断增强的处理能力和可用存储容量,对整个芯片的RLC网络矩阵进行仿真,并使用完全分布式和交叉耦合的封装模型。通过+执行全芯片扁平分析,RedHawk能够保持动态压降、EM和ESD的签核精确度。

Ø 经过芯片验证的签核精确度

在芯片级别,对工艺技术的使用往往受到以下一个或多个因素的驱动:更快的性能、更大的带宽、更高的性能功率比和更小的晶片尺寸。工艺技术越新,失败的几率越大,设计错误造成的代价也就越高。这便是签核认证如此重要的原因。

自2006年以来,TSMC和ANSYS工程师便在每个工艺技术方面展开紧密合作,确保ANSYS解决方案考虑到工艺的所有新规则、参数和要求,并确保其结果与测试芯片的参考结果保持一致。

ANSYS解决方案通过了先进的7nm工艺认证。ANSYS中能够支持认证的主要功能包括支持着色、多位多高度(MBMH)单元精确建模、特殊通过结构建模,以及相关的复杂电迁移(EM)规则。这个级别的认证标准有助于确保一次流片成功。

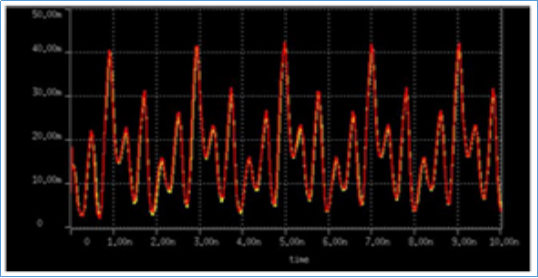

Ø 电源噪声对时序的影响

设计中的动态压降可能对时钟抖动、关键路径和时序产生影响。如今的设计拥有多个时钟和电源域,在签核前对时钟树的性能进行评估,识别并分析抖动、信号串扰和时序问题便非常重要。

RedHawk的快速全芯片级时序影响分析可帮助您评估时钟树性能。此外,它还支持您对可能受抖动、信号串扰和时序问题影响的电路零部件进行识别。RedHawk的SPICE精确签核仿真可帮助您识别时钟树、受影响的关键路径和电路时序的问题,并采取措施消除这些问题。

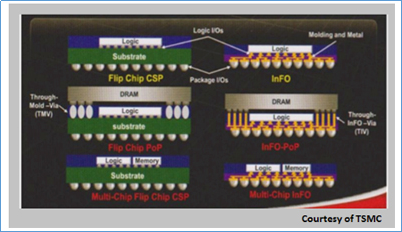

Ø 高级IC封装的完整性与可靠性

对包括片上系统(SoC)在内的集成电路(IC)设计师而言,有一个持续的策略,就是通过集成化和小型化,在增加性能和带宽的同时降低能耗和占用面积。

对于任何封装技术,完整性、可靠性和成本都是需要优化的三大主要因素。完整性因素涉及电源和信号噪声。可靠性涉及热、电迁移(EM)、静电放电(ESD)、电磁干扰(EMI)和热致结构应力问题。成本则涉及几乎所有应用,尤其是消费品和物联网(IoT)设备。在每种芯片的封装、电路板和系统的背景下优化和确保芯片(晶片级别)的完整性和可靠性,这非常复杂,并且涉及多个晶片时成本只会增加。

ANSYS解决方案使您能够确保您先进的2.5D或3D-IC封装设计可满足芯片、封装和系统级别的完整性和可靠性要求。

首页 > 产品中心 > 半导体仿真

首页 > 产品中心 > 半导体仿真