1、 文档目标

对 JTAG 接口有更多的认识,在遇到关于 JTAG 接口问题时有一些排查的思路。

2、 问题场景

在使用调试器过程时,免不了要接触到 JTAG 接口,当出现连接不上时,就不知道从哪来进行排查。

3、软硬件环境

1 )、软件版本:不涉及

2 )、电脑环境:不涉及

4、JTAG 接口介绍

1. JTAG 接口定义

JTAG(Joint Test Action Group,联合测试工作组),是一种国际标准测试协议,用于芯片内部测试。

标准的JTAG接口是4线:TMS模式选择、TCK时钟、TDI数据输入、TDO数据输出。

也包括一些测试复位,电源,地等。

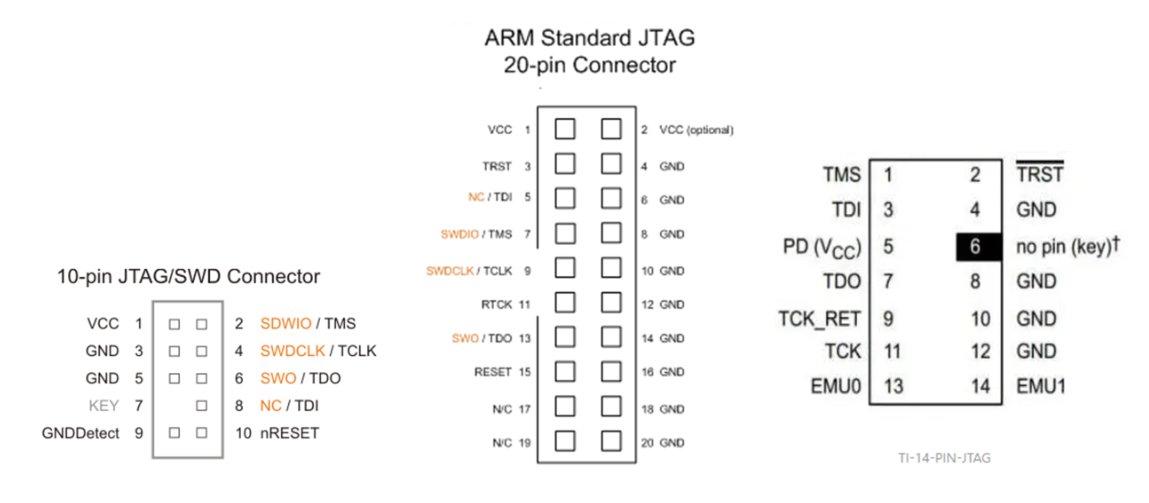

2. JTAG 接口的 10PIN 20PIN 14PIN

3. JTAG 接口作用

JTAG 接口的主要作用有三个,

a. 下载,即把程序下载到芯片的 flash 里或者外部存储器里。

b. 调试,实时调试程序的运行,控制程序全速执行,单步,断点等。

c. 边界扫描,获取芯片内部的信号逻辑状态及芯片引脚的状态。

4. JTAG 接口复用

在某些芯片上 JTAG 口和其他 GPIO 是复用的,就是在最开始烧写程序,之后就可以在程序运行的时候占用这个管脚,通常不会这么做,只有考虑成本用更少的芯片引脚时才这样做。

需要在烧写程序的时候保证芯片在复位状态下,然后才能正确识别 JTAG。

5. JTAG 接口问题与排查

1)、在使用 JTAG 调试时,首先要排查的是硬件的连接和供电问题。

例如找不到目标板:

https://alidocs.dingtalk.com/i/nodes/ZgpG2NdyVXrKBv1YTRqRwqp48MwvDqPk?doc_type=wiki_doc#

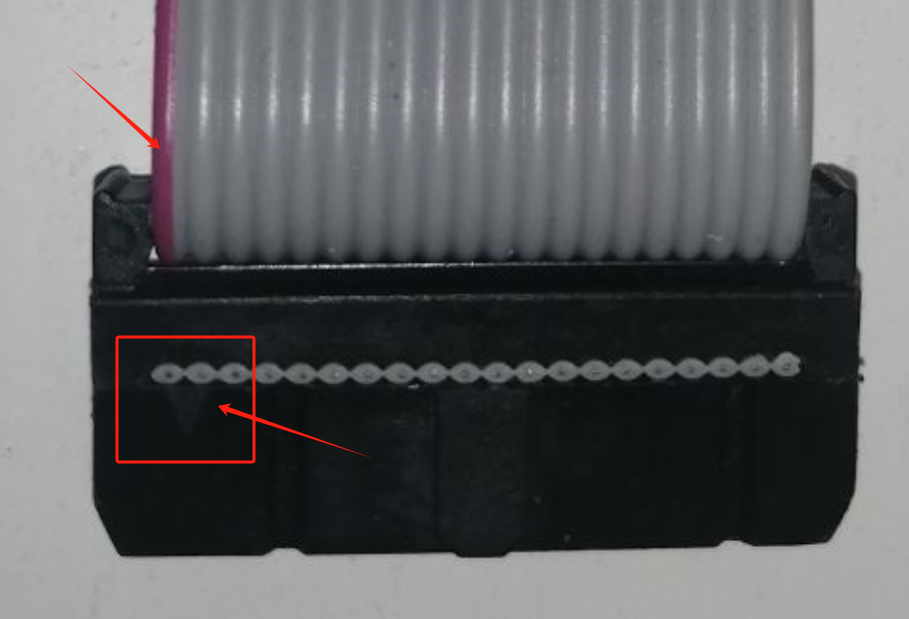

2)、另外还有一种是对于实物接口的线序不清楚,如图 1 ,通常这种排线,红线为 1 脚,同时在座上可以看到一个倒三角标记,也表示是 1 脚。

图 1

如图 1 ,通常这种排线,红线为 1 脚,同时在座上可以看到一个倒三角标记,也表示是 1 脚。

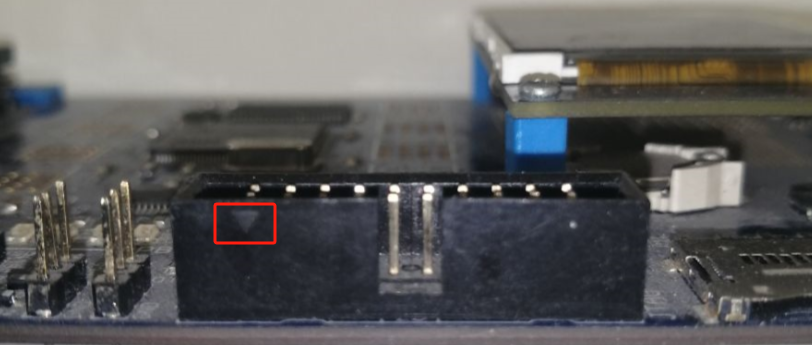

图 2

如图 2 ,通常这种排座,也可以看到一个倒三角标记,表示是 1 脚。确定了 1 脚位置之后,再排查接口的线序是不是正确。

3)、再有就是关于接口的上下拉问题。

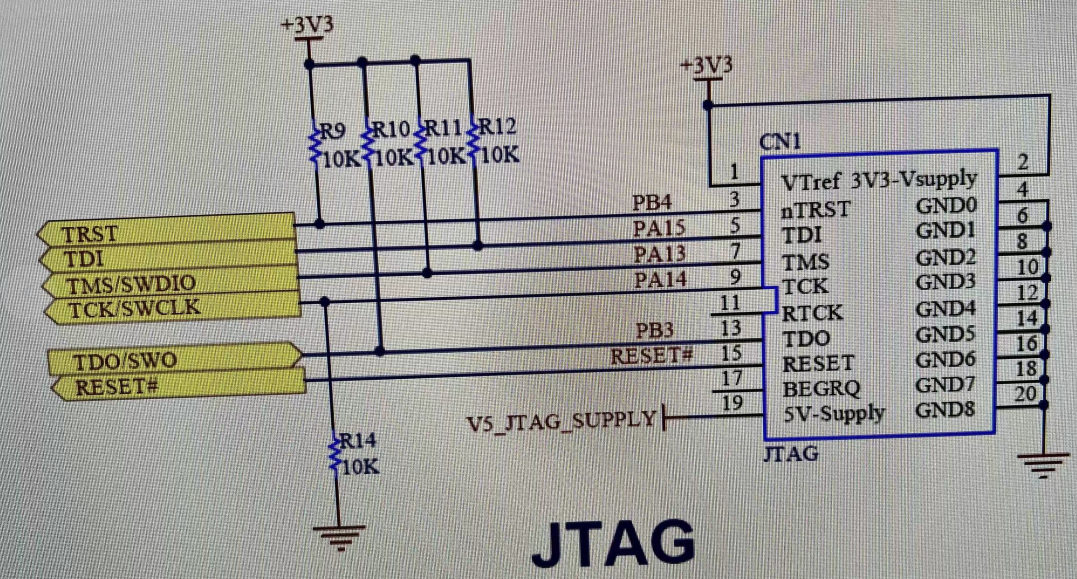

图 3

通常是不需要对 JTAG 口进行上拉或下拉的,某些仿真器为了保证初始状态的确定性会有一些要求,一般参考图 3。

6. 其他调试接口

a. SWD

串行调试(Serial Wire Debug),需要4个SWDIO和SWCLK 及电源和地(或者5个,增加 SWO)引脚。

SWDIO(Serial Wire Debug Input/Output)是SWD接口中最重要的线之一。它既是数据线,也是控制线。在调试过程中,SWDIO用于传输调试信息和数据,同时还负责传输控制信号。

SWCLK(Serial Wire Debug Clock)是SWD接口中的时钟线,用于同步SWDIO线上的数据传输。

SWO(Serial Wire Output)是SWD接口中的输出线,用于将处理器内部的跟踪信息输出到外部调试器。

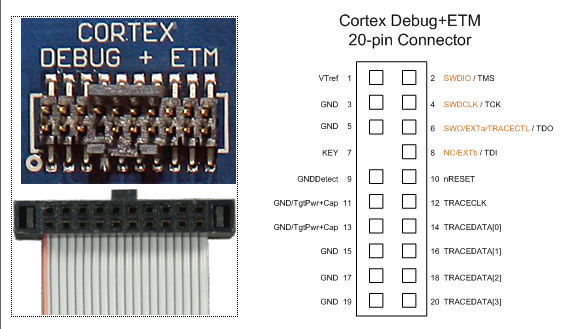

b. Cortex Debug+ETM

ETM指令跟踪。(TRACEDATA[0..3])上输出数据,(TRACECLK)用于跟踪时钟。

首页 > 资源中心 > FAQ

首页 > 资源中心 > FAQ