1、 文档目标

解决由于丝印重叠导致的制造设计(DFM)问题。

2、 问题场景

丝印重叠阻焊的影响有如下:

1)PCB板后期打样,一般是以阻焊层优先,如果丝印跟焊盘重叠,那么就会优先选择焊盘,重叠在焊盘上的丝印就会被消除。

2)丝印附在焊盘上会影响后期的焊接,焊盘表面上会被盖上油墨,存在绝缘作用影响后期上锡。

Atium Designer 23.6 开始引入”丝印制备“的功能,为整个PCB设计上快速精确定位丝印。避免大量的手动操作和未被检查到的问题。

3、软硬件环境

1)、软件版本:Altium Designer 23.6 以上支持

2)、电脑环境:Windows 11

3)、外设硬件:无

4、解决方法

PCB 封装库

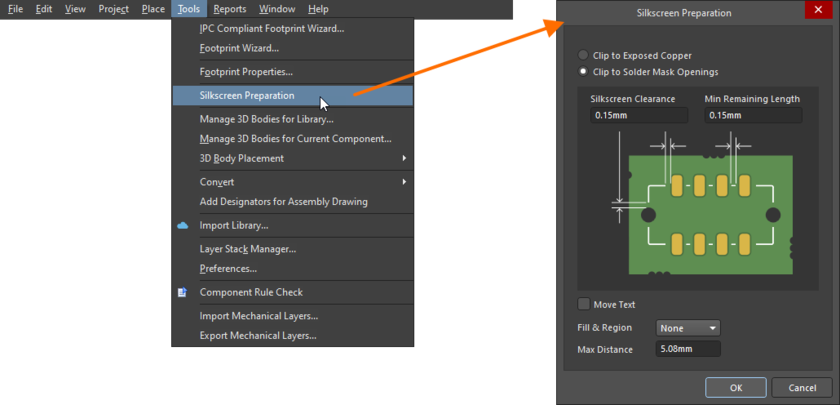

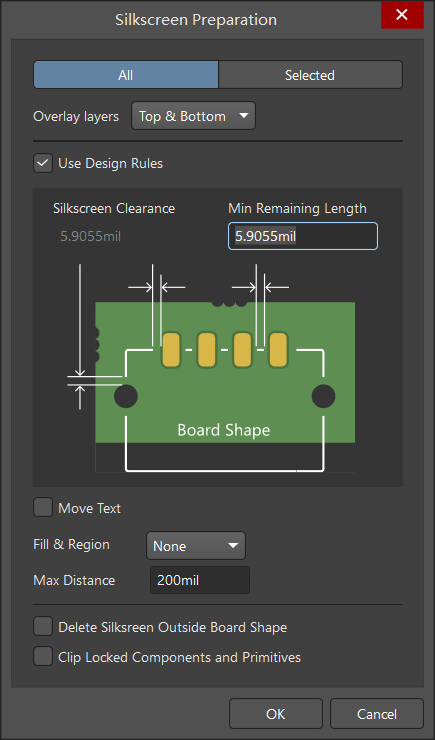

菜单栏下打开:【Tools】→【Silkscreen Preparation】,将丝印制备对话框打开。

图 1

Clip to Exposed Copper/Clip to Solder Mask Openings :勾选根据铜层裁剪或者阻焊层裁剪,根据制作要求设置裁剪间距;

Move Text:在有文本字符串情况下,进行勾选。可以将丝印文本字符串从铜层/阻焊层重叠移开。移动受【Max Distance】值的约束。

Fill & Region :在有Fill & Region情况下,可以选择三种模式:

1、None 不做处理;2、Clip 进行裁剪;3、Move 进行移动,受【Max Distance】值的约束。

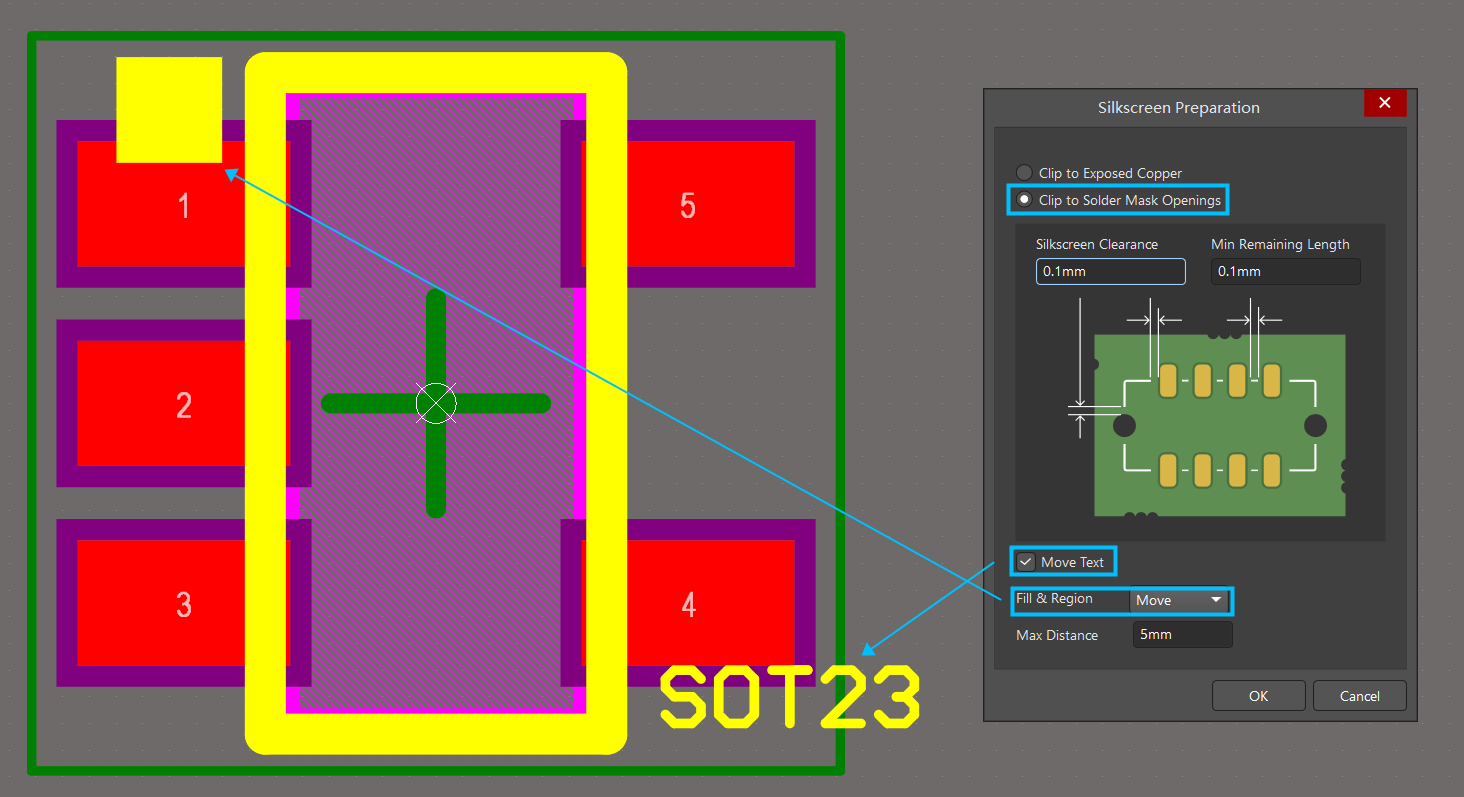

图 2

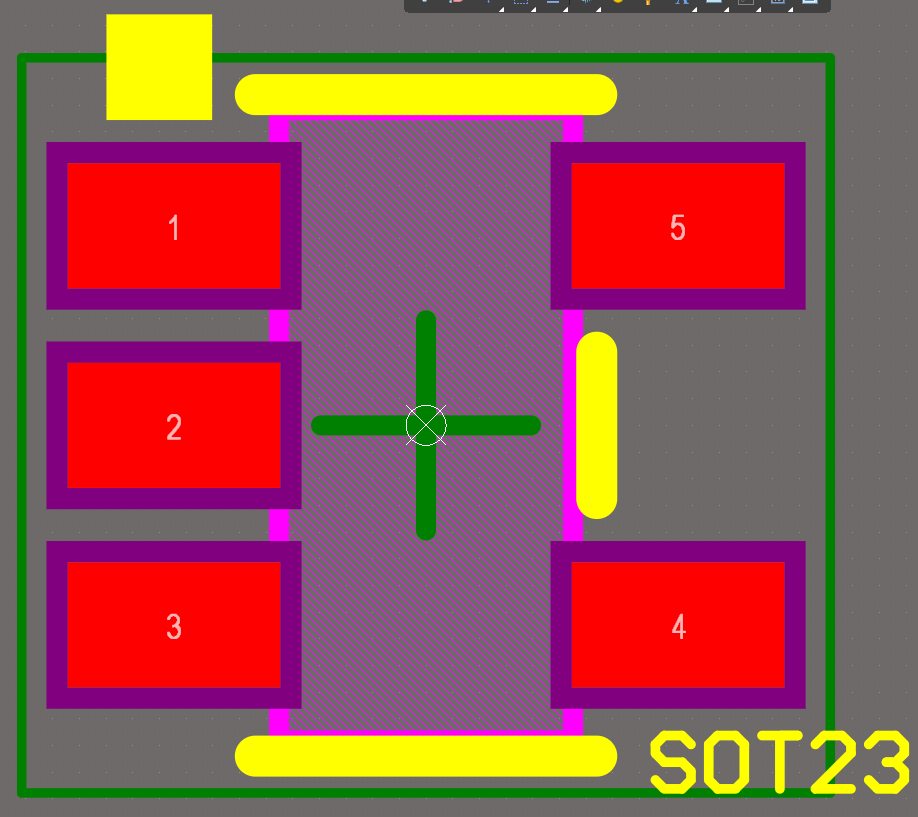

效果如下

图 3

PCB 编辑器

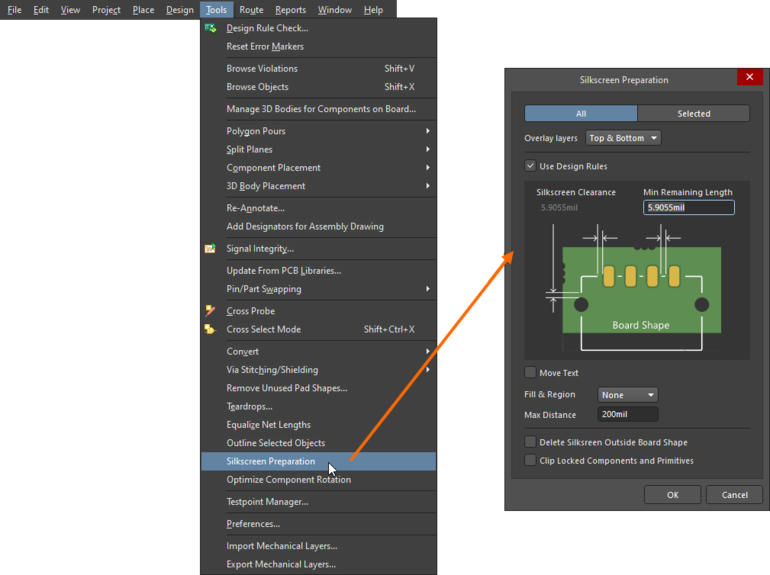

菜单栏下打开:【Tools】→【Silkscreen Preparation】,将丝印制备对话框打开。

图 4

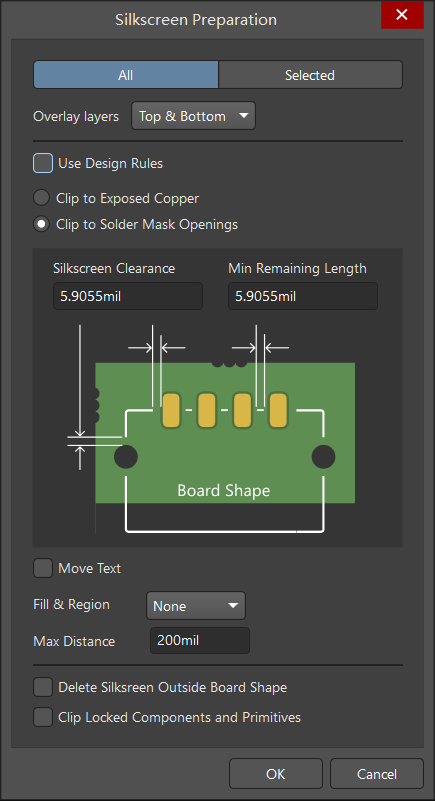

第一栏:设置即是将丝印制备适用于哪些元素对象的选择,【All】选项为所有对象,【Selected】选项为仅在设计中选择的对象,此处一般默认【All】适用于所有对象设置。

第二栏:Overlay layers 设置即为丝印制备命令执行的层范围选择,点击下滑栏可以选择单独的【TOP】、【Bottom】或者【TOP&Bottom】选项,推荐默认设置为【TOP&Bottom】选项,让其命令在顶底丝印层都可进行实现。

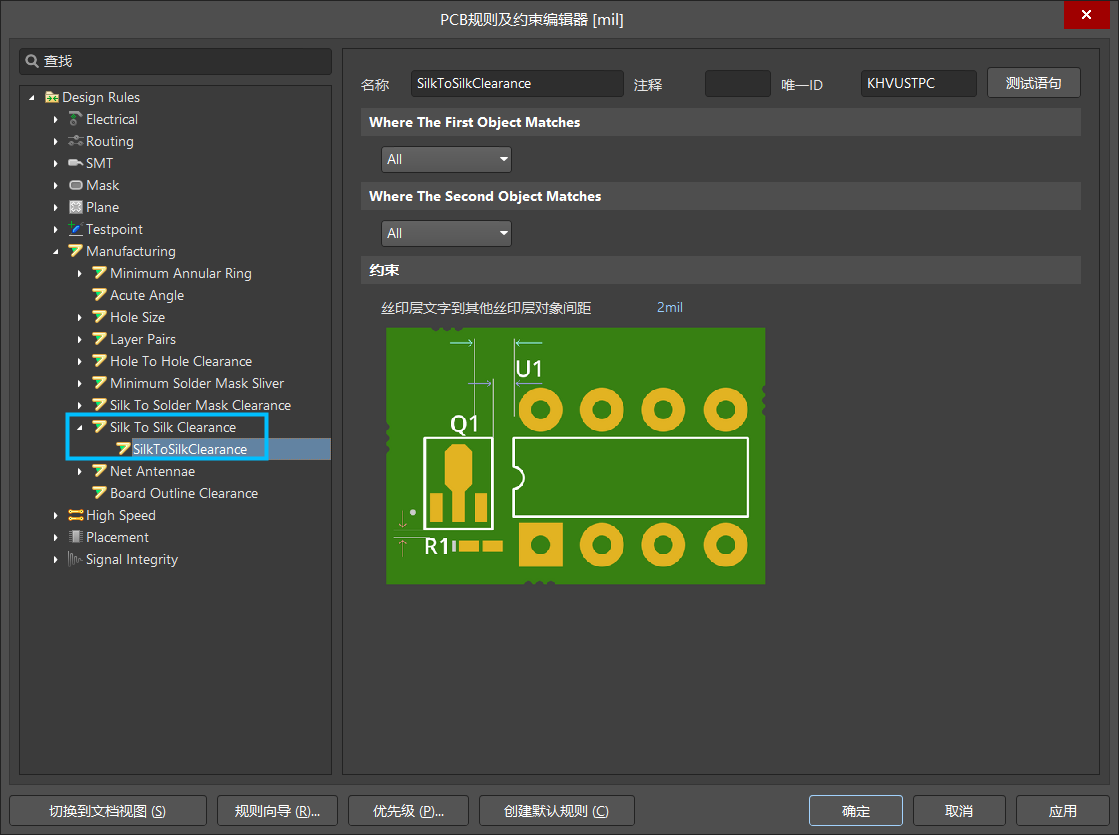

第三栏:勾选【Use Design Rules】选项,那么丝印制备则是按照【PCB规则及约束编辑器】对话框内的丝印跟丝印层对象间距规则进行执行。

图 5

如果不勾选【Use Design Rules】选项,那么就需要根据 PCB 设计要求手动选择丝印避让的对象,两种方式选择:【Clip to Exposed Copper】、【Clip to solder Mask Openings】选择铜层或者阻焊层的设置模式,可根据具体设计进行选择,推荐设置为【Clip to solder Mask Openings】选择完模式之后即可设置丝印间距,间距受【Max Distance】值的约束。

第四栏:勾选【Move Text】选项,一般在PCB设计完成之后是需要调整器件位号丝印不要覆盖在焊盘上,所以需要将【Move Text】选项进行勾选,间距受【Max Distance】值的约束。

第五栏:【Fill & Region】在有Fill & Region情况下,可以选择三种模式:

1、None 不做处理;2、Clip 进行裁剪;3、Move 进行移动,受【Max Distance】值的约束。

第六栏:【Delete Silksreen Outside Board Shape】选项即为是否需要自动移除板框外部的丝印。

第七栏:【Clip Locked Components ang Prinitives】选项即为丝印制备针对PCB设计中锁定的器件是否实行变更

处理。

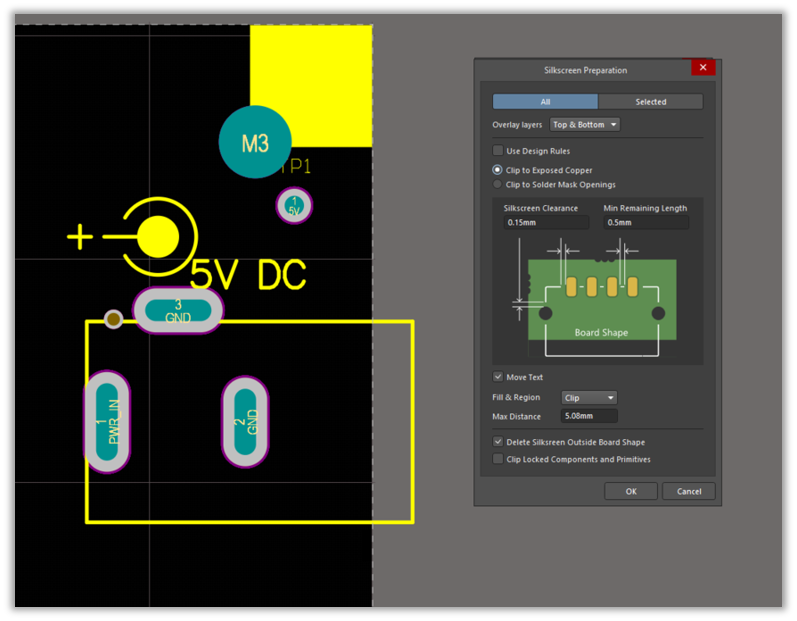

图 6

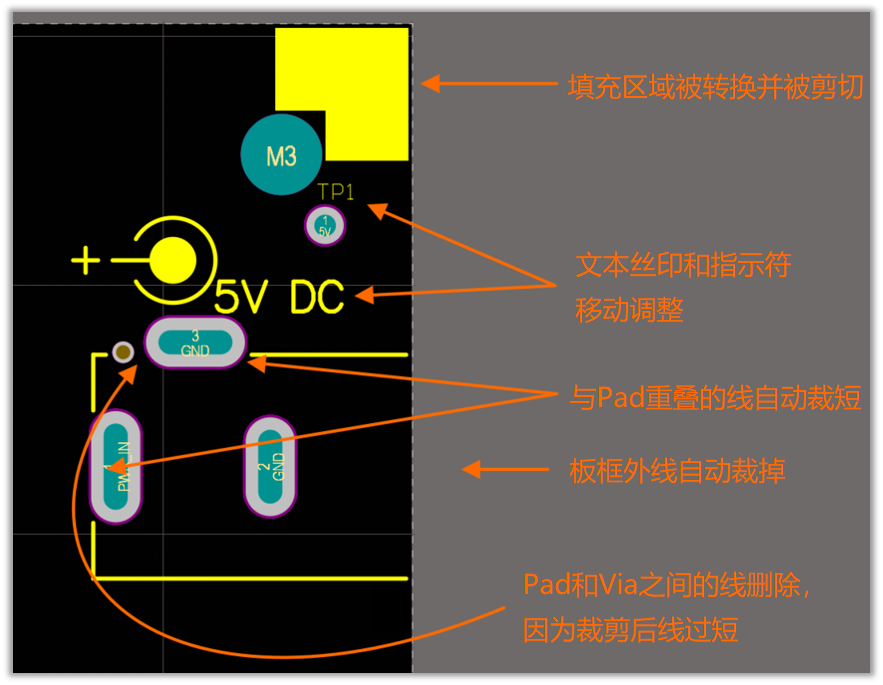

效果如下:

图 7

首页 > 资源中心 > FAQ

首页 > 资源中心 > FAQ